**Universidade Federal do Espírito Santo**

Diego Rossi Mafioletti

A Place-as-you-go In-network Framework by Modular Decomposition for Flexible Embedding to Software/Hardware Co-design

Vitória-ES

2023

## A Place-as-you-go In-network Framework by Modular Decomposition for Flexible Embedding to Software/Hardware Co-design

### Diego Rossi Mafioletti

Tese de Doutorado submetida ao Programa de Pós-Graduação em Informática da Universidade Federal do Espírito Santo como requisito parcial para a obtenção do grau de Doutor em Ciência da Computação.

Aprovada em 21 de Outubro de 2022.

Magnos Martinello

Prof. Dr. Magnos Martinello Orientador, participação remota

Prof. Dr. Moisés Renato Nunes Ribeiro Coorientador, participação remota

Prof. Dr. Vinícius Fernandes Soares Mota Membro Interno, participação remota

Prof. Dr. Cristiano Bonato Both Membro Externo, participação remota

Prof. Dr. Fabio Luciano Verdi Membro Externo, participação remota

Prof. Dr. Paolo Giaccone Membro Externo, participação remota

UNIVERSIDADE FEDERAL DO ESPÍRITO SANTO Vitória/ES, 21 de Outubro de 2022.

#### UNIVERSIDADE FEDERAL DO ESPÍRITO SANTO

#### **PROTOCOLO DE ASSINATURA**

O documento acima foi assinado digitalmente com senha eletrônica através do Protocolo Web, conforme Portaria UFES nº 1.269 de 30/08/2018, por MAGNOS MARTINELLO - SIAPE 1669875 Departamento de Informática - DI/CT Em 21/10/2022 às 14:50

Para verificar as assinaturas e visualizar o documento original acesse o link: https://api.lepisma.ufes.br/arquivos-assinados/588939?tipoArquivo=O

Ficha catalográfica disponibilizada pelo Sistema Integrado de Bibliotecas - SIBI/UFES e elaborada pelo autor

Rossi Mafioletti, Diego, 1979-

R833p A place-as-you-go in-network framework by modular decomposition for flexible embedding to software/hardware co design / Diego Rossi Mafioletti. - 2022. 132 f. : il.

> Orientador: Magnos Martinello. Coorientador: Moises Renato Nunes Ribeiro. Tese (Doutorado em Informática) - Universidade Federal do Espírito Santo, Centro Tecnológico.

1. Redes de computadores. 2. Interconexão em rede (Telecomunicações). 3. Linguagem de programação de domínio específico (Computadores). 4. Sistemas embarcados (Computadores). 5. Sistemas de computação virtual. I. Martinello, Magnos. II. Nunes Ribeiro, Moises Renato. III. Universidade Federal do Espírito Santo. Centro Tecnológico. IV. Título.

CDU: 004

Dedico este trabalho à minha família e amigos.

## Resumo

A computação em nuvem tornou-se muito popular como plataforma computacional, fazendo parte do cotidiano das pessoas. Para fornecer o poder de supercomputação exigido pela nuvem, a rede deve desempenhar um papel crucial ao conectar centenas de milhares de máquinas nos *data centers*. No entanto, com o surgimento de um novo conjunto maciço de aplicativos intensivos e nativos da nuvem (por exemplo, 5G, robótica em nuvem, aprendizado profundo, etc.) combinado com a virtualização de funções de rede (NFV), uma pressão significativa foi colocada sobre a capacidade de processamento das CPUs dos servidores, exigindo ainda mais alta performance e transformando a rede em um gargalo.

Normalmente, a interface de rede (NIC) é usada para conectar servidores à rede. No entanto, as interface de rede inteligentes (SmartNICs) estão se tornando um método cada vez mais popular de descarregar tarefas intensivas de processamento de pacotes dos servidores, liberando ciclos da CPU e impulsionando o desempenho de aplicativos.

O desafio chave para o uso de uma SmartNIC é como fazer uso eficiente desses recursos de computação heterogêneos na rede, pois há uma lacuna significativa entre o aplicativo e os recursos de computação dos dispositivos programáveis. Em primeiro lugar, este dispositivo carece de modelos genéricos de programação ou abstrações, sendo geralmente programado usando primitivas de baixo nível ou APIs proprietárias. Em segundo lugar, o desenvolvedor de rede precisa lidar com a complexidade interna dos recursos de hardware, bem como gerenciar o equilíbrio nas cargas de trabalho de descarregamento, tentando descobrir o balanço entre sobrecargas adicionais e benefícios do descarregamento. É necessário descobrir como co-projetar a lógica do aplicativo entre o hardware de rede programável e os servidores dentro do paradigma de computação de borda.

Esta tese apresenta um novo arcabouço para prototipagem e implantação de aplicativos em rede. Ele é estruturado em um conjunto de componentes que dependem de i) decomposição funcional da aplicação; ii) identificação dos blocos lógicos; iii) agregação de funções sobrepostas mescladas e mapeadas em funcionalidades de rede em linguagem P4; iv) interceptar, interagir e encaminhar com estruturas de dados para balancear o descarregamento de fluxos de rede.

A fim de demonstrar o princípio de co-design em várias aplicações, funções de rede virtual (VNFs) são criadas, e alguns de seus elementos funcionalmente decompostos são implantados como pequenas funções de rede incorporadas (eNFs) em processadores de rede em diversos casos de uso, revisando os componentes do arcabouço levantados anteriormente: decompondo funções de rede (i, ii, iii) e unificando componentes para se encaixarem em um conjunto de VNFs/eNFs, examinando latência, taxa de transferência e uso de vCPU em relação à sua contraparte implementada em software; interceptando e interagindo com robótica em nuvem (iv), abordando preocupações de segurança ao usar planos de dados programáveis; evoluindo para funções de rede seguras executadas em computação em rede (i, ii, iii, iv), verificando o overhead adicionado por elas; e modificando um mecanismo de escalonador *upstream* em PON (iv), fornecendo requisitos de baixa latência a aplicativos.

**Palavras-chave:** Computação em Rede, Co-design de hardware/software, Virtualização de Funções de Rede, Computação de Borda, Paradigma 5G.

## Abstract

Cloud computing has become very popular as a computation platform, being part of people's daily life. In order to deliver the cloud-required super-computing power, the network must play a crucial role by connecting hundreds of thousands of machines within data centres. However, with the rise of a new massive set of cloud-native and intensive applications (e.g. 5G, cloud robotics, deep learning, etc) combined with network function virtualisation (NFV), a significant strain has been placed on the processing capacity of server CPUs, demanding even higher performance and turning the network into a bottleneck.

Typically, the network interface card (NIC) has been used to connect servers to the network. Although, smart network interface cards (SmartNICs) are becoming an increasingly popular method of offloading intensive packet processing tasks from servers, thus freeing CPU cycles to drive application performance.

The critical challenge towards using a SmartNIC is how to make efficient use of these in-network heterogeneous computing resources, as there is a significant gap between application software and the computing capabilities of programmable devices. First, this device lacks generic programming models or abstractions, being usually programmed using low-level primitives or proprietary APIs. Second, the network developer needs to deal with the internal complexity of hardware resources, as well as manage the balance on offloading workloads, trying to find out the tradeoff between additional overheads and offloading benefits. It is needed to figure out how to co-design application logic between programmable network hardware and end-host servers within the edge computing paradigm.

This thesis presents a novel framework for prototyping and deploying in-network applications. The framework is structured into a set of components that rely on i) application functional decomposition; ii) identification of logic blocks; iii) aggregation of overlapped functions merged and mapped on network functionalities in P4 language; iv) intercepting, interacting and forwarding with data structures for balancing the offloading of network flows.

In order to demonstrate the principle of co-designing on diverse applications, Virtual Network Functions (VNFs) are created, and some of their functionally decomposed elements are deployed as small embedded Network Functions (eNFs) on in-network processors in sorted use cases, reviewing the framework components raised previously: decomposing network functions (i, ii, iii) and unifying components to fit into a set of VNFs/eNFs, examining latency, throughput and vCPU usage against their software implementation counterpart; intercepting and interacting with cloud robotics (iv), raising security concerns when using programmable data planes; evolving to security network functions running at in-network computing (i, ii, iii, iv), checking the overhead added by them; and modifying a PON upstream scheduler mechanism (iv), providing low latency requirements for applications.

**Keywords:** In-Network Computing, Hardware/Software Co-design, Network Functions Virtualisation, Edge computing, 5G paradigm.

# **List of Figures**

| 1.1<br>1.2 | Architectural options to In-Network Computing for packets processing.<br>Correlation between the main topics and publications of the thesis with | 11 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2        | the intersection between them                                                                                                                    | 15 |

| 2.1        | Edge computing paradigm. Source [Shi and Dustdar 2016]                                                                                           | 19 |

| 2.2        | A typical PON architecture.                                                                                                                      | 20 |

| 2.3        | PON DBA abstraction [ITU-T 2014].                                                                                                                | 21 |

| 2.4        | CU/DU-based C-RAN architecture [Ahmadi 2019]                                                                                                     | 21 |

| 2.5        | NFV implementation of network functions using virtualisation tech-                                                                               |    |

|            | niques over standard hardware. Source: [Han et al. 2015]                                                                                         | 24 |

| 2.6        | SmartNIC architecture simplified block diagram                                                                                                   | 26 |

| 2.7        | Traditional switches vs. programmable switches                                                                                                   |    |

|            | [The P4 Language Consortium 2021]                                                                                                                | 27 |

| 2.8        | Portable Switch Pipeline [The P4.org Architecture Working Group 2020].                                                                           | 27 |

| 2.9        | Packet paths in PSA [The P4.org Architecture Working Group 2020].                                                                                | 28 |

| 2.10       | 0 Match-Action Unit Dataflow. [The P4 Language Consortium 2021]                                                                                  | 28 |

| 2.1        | 1 Programming a target with P4 [The P4 Language Consortium 2021].                                                                                | 29 |

| 2.12       | 2The architecture of ClickNP [Kun et al. 2016]                                                                                                   | 30 |

| 2.13       | 3The SmartNIC GFT architecture, showing the flow of exception packets                                                                            |    |

|            | from the FPGA to software to establish a flow offloaded in hardware                                                                              |    |

|            | [Firestone et al. 2018]                                                                                                                          | 32 |

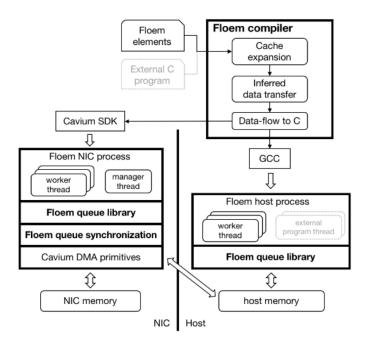

| 2.14       | 4FLOEM system architecture. [Phothilimthana et al. 2018]                                                                                         | 33 |

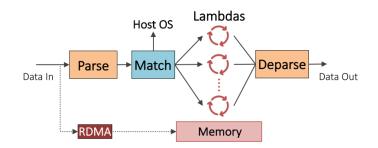

|            | $5\lambda$ -NIC's abstract machine model. [Choi et al. 2019]                                                                                     | 34 |

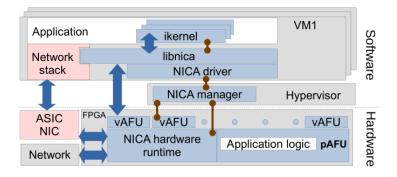

| 2.16       | 6NICA overview. [Eran et al. 2019]                                                                                                               | 35 |

| 2.1        | 7An overview of the iPipe runtime on the programmable NIC                                                                                        |    |

|            | [Liu et al. 2019].                                                                                                                               | 36 |

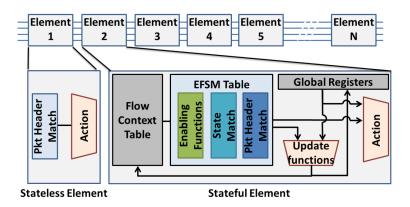

| 2.18       | 8FlowBlaze machine model. [Pontarelli et al. 2019]                                                                                               | 37 |

| 2.19       | 9FairNIC sharing resources between two tenants. [Grant et al. 2020].                                                                             | 38 |

| 2.20       | OProgramming a target with P4 [The P4.org API Working Group 2020]                                                                                | 39 |

|            | 1 Overview of the EP4 architecture [Karrakchou et al. 2021]                                                                                      | 40 |

| 2.22       | 2The DPPx system architecture [Osinski et al. 2019]                                                                                              | 41 |

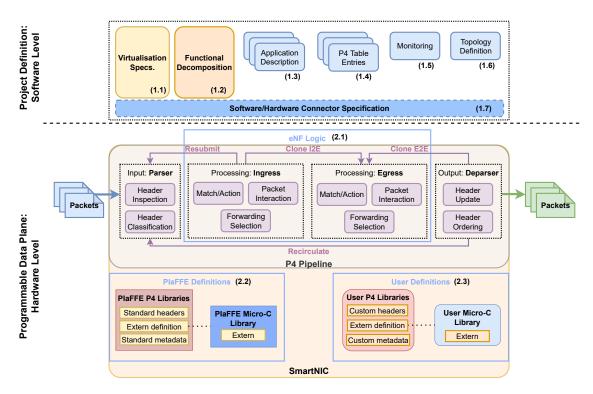

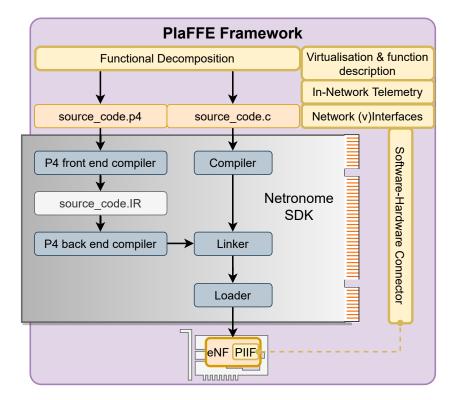

| 3.1        | PIaFFE framework architecture.                                                                                                                   | 47 |

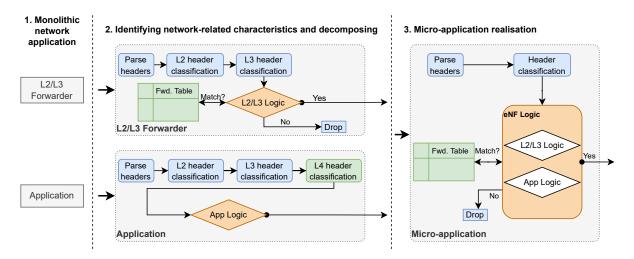

| 3.2        | Illustrative example of functional decomposition using a set of network                                                                          |    |

|            | applications                                                                                                                                     | 49 |

| 3.3        |                                                                                                                                                  |    |

|            | element.                                                                                                                                         | 50 |

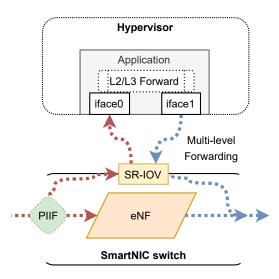

| 3.4        | Architectural options for PIaFFE.                                                                                                                | 52 |

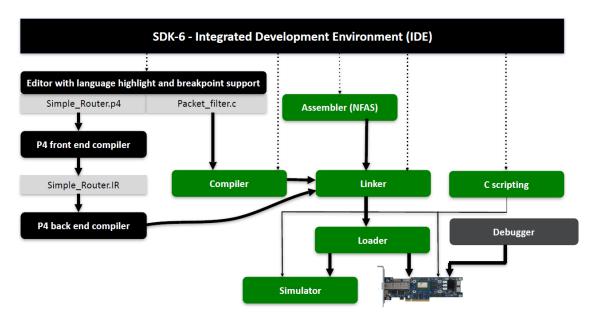

|            | Netronome P4 SDK architecturePIaFFE framework building blocks                                                 | 53<br>53 |

|------------|---------------------------------------------------------------------------------------------------------------|----------|

| 3.7        | Resumed steps for embedding applications into a programmable net-<br>work device using the PIaFFE framework   | 56       |

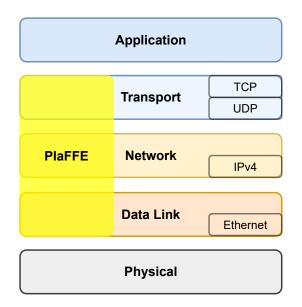

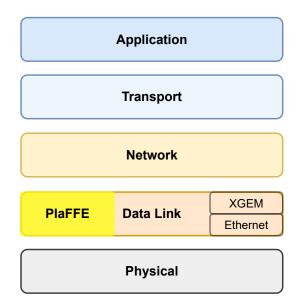

| 4.1<br>4.2 | Network layers handled by PIaFFE in this Chapter                                                              | 60       |

|            | [Rahman Chowdhury et al. 2019].                                                                               | 61       |

| 4.3        | Modular eNFs and P4 logic mapping for network functionalities                                                 | 61       |

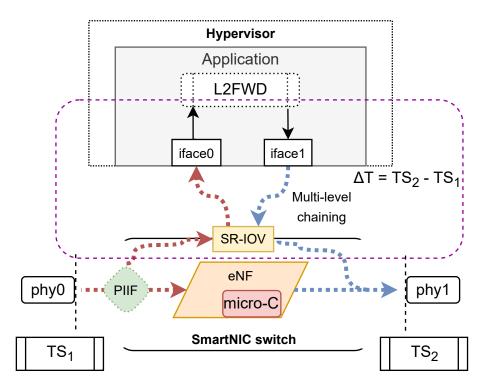

|            | Multi-level Chaining of Network Functions                                                                     | 62       |

| 4.5        | [Canada et al. 2017]                                                                                          | 64       |

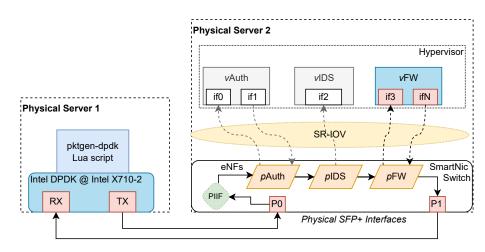

|            | Prototype implementation and testbed.                                                                         | 66       |

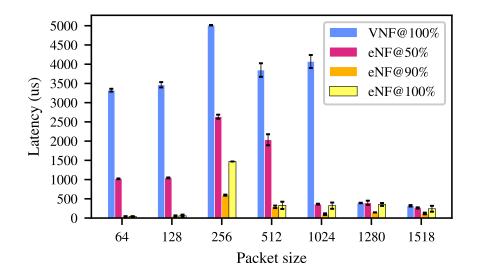

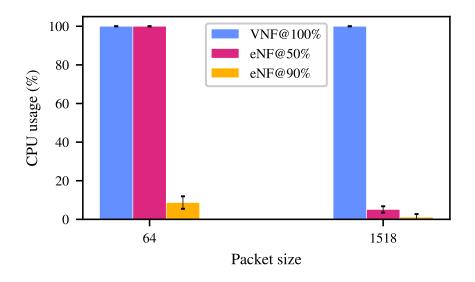

|            | Latency comparison for different scenario types.                                                              | 67       |

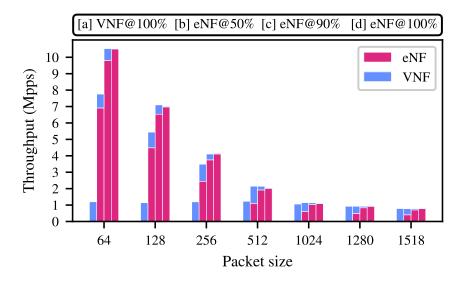

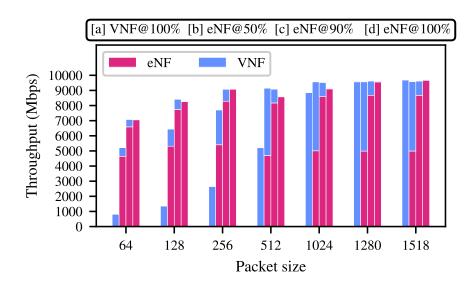

|            | Throughput in Millions of Packets per Second (Mpps)                                                           | 68<br>68 |

|            | VNF CPU usage for two extreme packet sizes.                                                                   | 69       |

|            |                                                                                                               |          |

|            | Cloud Robotics and Programmable Data Plane                                                                    | 72<br>73 |

|            | PIaFFE and multi-level chaining concept.                                                                      | 73       |

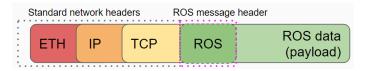

| 5.4        | Network packet headers, ROS message header and ROS data                                                       | 74       |

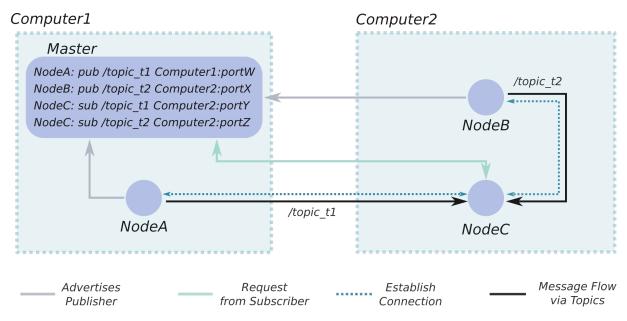

| 5.5        | ROS operation: the master registers and provides information for pub-                                         |          |

|            | lishers and subscribers to establish connections and allow nodes to exchange information directly via topics. | 76       |

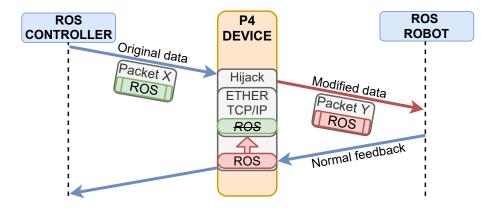

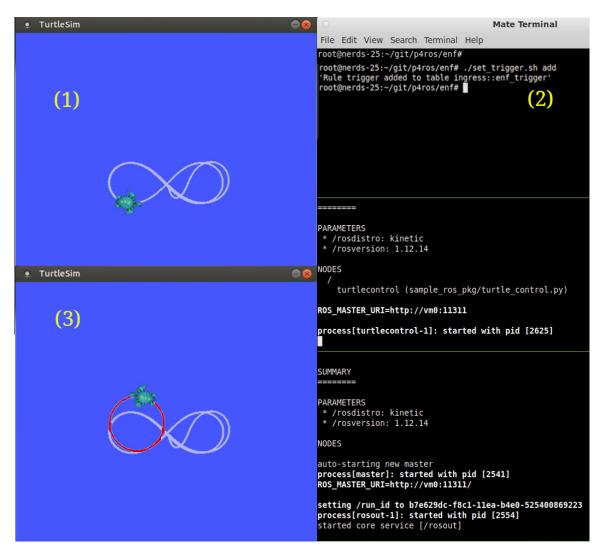

| 5.6        | Threat model: hijacking.                                                                                      | 78       |

| 5.7        | TurtleSim robot simulator: (1) Normal robot behaviour; (2) Setting a                                          |          |

|            | trigger via P4 table; (3) Abnormal robot behaviour (red track)                                                | 79       |

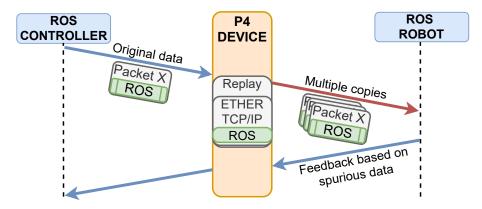

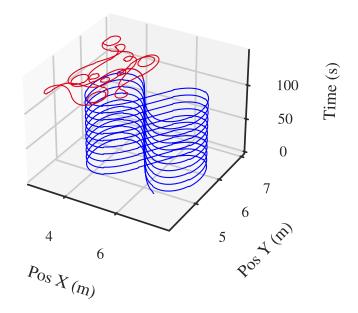

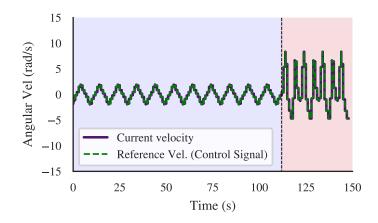

| 5.8<br>5.9 | Threat model: replay attack                                                                                   | 80       |

| 5.9        | (blue) versus disturbed (red) operation                                                                       | 81       |

| 5.10       | Replay attack: angular velocity of the robot under normal operation                                           |          |

|            | (blue zone) and under attack (red zone); the red dashed line marks the                                        | ~~       |

| 5 1 1      | beginning of the attack                                                                                       | 82       |

| 5.11       | (blue zone) and under attack (red zone); the red dashed line marks the                                        |          |

|            | beginning of the attack.                                                                                      | 82       |

| 6.1        | Network layers handled by PIaFFE in this Chapter.                                                             | 86       |

| 6.2        | Illustrative example of decomposition using a set of network applications.                                    |          |

| 6.3        | Multi-level forwarding using Intercepting and Forwarding (PIIF) element.                                      |          |

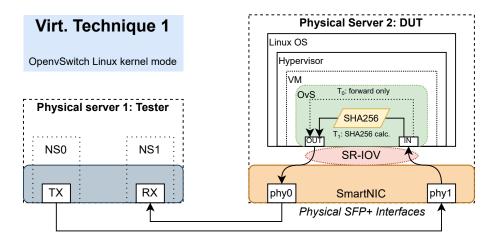

|            | Virtualisation techniques: Open vSwitch software switch                                                       | 91<br>01 |

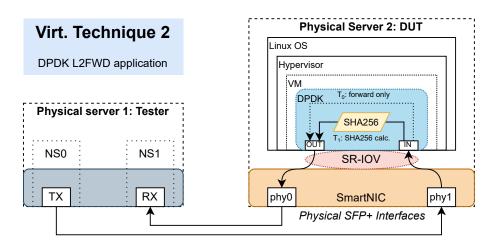

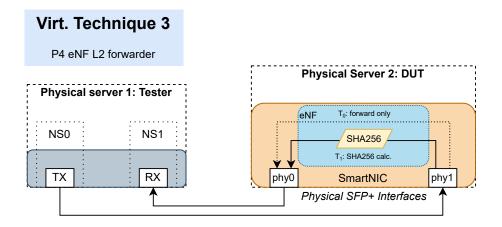

|            | Virtualisation techniques: Intel DPDK L2 forwarder application Virtualisation techniques: P4-enabled hardware | 91<br>92 |

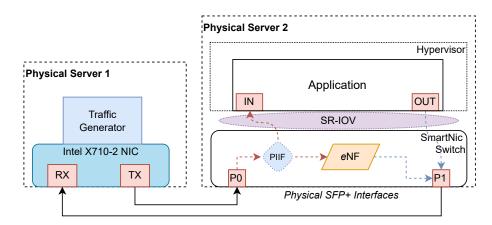

|            | Testbed specification: Prototype implementation and testbed.                                                  | 92       |

| 6.8        | Using hardware timestamp to measure the time to process/deliver a                                             |          |

|            | packet                                                                                                        | 93       |

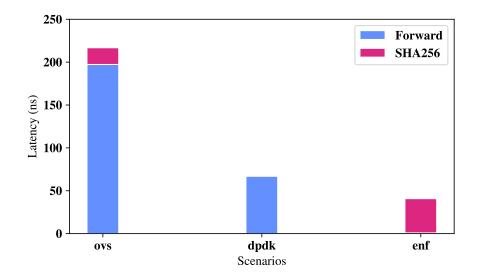

| 6.9  | Latency (Processing and forwarding) for software and hardware micro-<br>applications running SHA-256 algorithm and network forwarding: Total<br>latency using different types of forwarding/calculation virtualisation |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | techniques.                                                                                                                                                                                                            | 95  |

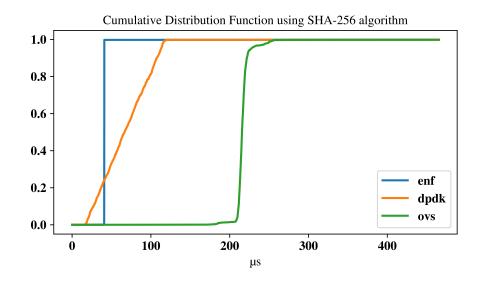

| 6.10 | Cumulative Distribution Function (CDF) Probability for SHA-256 calcu-                                                                                                                                                  |     |

|      | lation and forwarding.                                                                                                                                                                                                 | 95  |

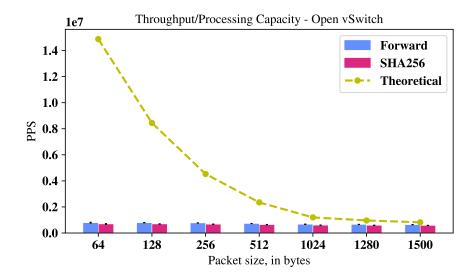

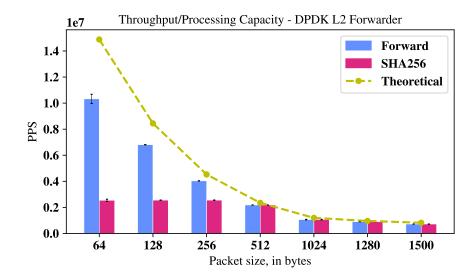

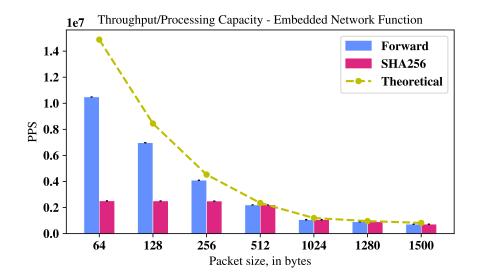

| 6.11 | l Packet processing capacity comparison between software and hardware                                                                                                                                                  |     |

|      | micro-applications running SHA-256 algorithm, using different packet                                                                                                                                                   |     |

|      | sizes and virtualisation techniques: Open vSwitch (OVS) software switch.                                                                                                                                               | 96  |

| 6.12 | 2Packet processing capacity comparison between software and hardware<br>micro-applications running SHA-256 algorithm, using different packet                                                                           |     |

|      | sizes and virtualisation techniques: DPDK application                                                                                                                                                                  | 96  |

| 6.13 | BPacket processing capacity comparison between software and hardware                                                                                                                                                   | 00  |

|      | micro-applications running SHA-256 algorithm, using different packet                                                                                                                                                   |     |

|      | sizes and virtualisation techniques: embedded network function with                                                                                                                                                    |     |

|      | P4 in NIC                                                                                                                                                                                                              | 97  |

| 7.1  | Network layers handled by PIaFFE in this Chapter.                                                                                                                                                                      | 101 |

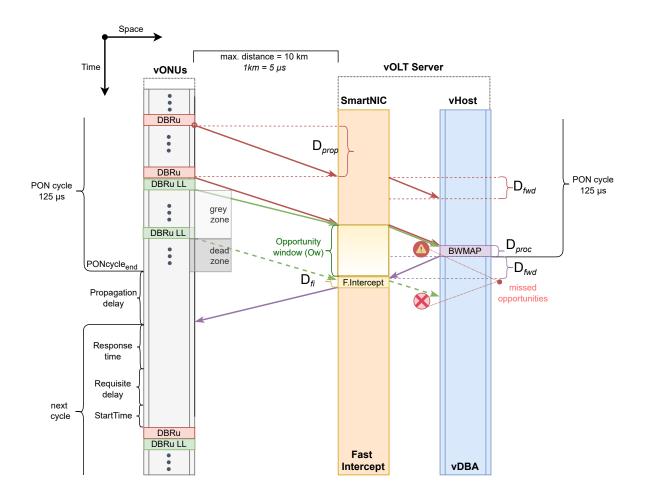

| 7.2  | Fast Intercept concept.                                                                                                                                                                                                | 103 |

| 7.3  |                                                                                                                                                                                                                        | 105 |

| 7.4  | Proposed dual-DBA process with P4 in-NIC computing.                                                                                                                                                                    | 106 |

| 7.5  | Multi-level DBA scheduling provided by In-Network Computing                                                                                                                                                            | 107 |

| 7.6  | Fast Intercept rescheduling mechanism.                                                                                                                                                                                 | 108 |

| 7.7  | P4 Parser and Ingress pipelines                                                                                                                                                                                        | 108 |

|      | Comparison between multiple approaches to calculating the DBA algo-                                                                                                                                                    |     |

|      | rithm                                                                                                                                                                                                                  | 109 |

| 7.9  | Dissecting the algorithm: times of each step                                                                                                                                                                           | 110 |

# **List of Tables**

# **List of Codes**

| 3.1 | P4 source code of the PIIF                     | 51 |

|-----|------------------------------------------------|----|

| 4.1 | P4 source code example of an Offload Balancer  | 63 |

| 6.1 | Pseudo code of the PIIF                        | 88 |

| 6.2 | A fragment of micro-C extern SHA-256 function. | 89 |

# List of abbreviations and acronyms

- ASIC Application-Specific Integrated Circuit

- CDN Content Delivery Network

- DBA Dynamic Bandwidth Allocation

- DC Data Centre

- eNF Embedded Network Function

- IaaS Infrastructure as a Service

- INC In-Network Computing

- MEC Multi-Access Edge Computing

- National Institute of Standards and Technology NIST

- NF Network Function

- NFV Network Function Virtualisation

- NIC Network Interface Card

- PaaS Platform as a Service

- PIIF PIaFFE Intercepting and Forwarding

- QoE Quality of Experience

- QoS Quality of Service

- RAN Radio Access Network

- SaaS Software as a Service

- SFC Service Function Chain

- SHA Secure Hash Algorithm

- SR-IOV Single Root I/O Virtualisation

- VNF Virtual Network Functions

# Contents

| 1 | Int | roduction                                                       | 10 |

|---|-----|-----------------------------------------------------------------|----|

|   | 1.1 | Research Question                                               | 12 |

|   | 1.2 | Hypotheses                                                      | 13 |

|   | 1.3 | Objectives                                                      | 14 |

|   | 1.4 | Contributions                                                   | 14 |

|   | 1.5 | Text Structure                                                  | 16 |

| 2 | Fou | indations and State-of-the-Art                                  | 18 |

|   | 2.1 | Background                                                      | 18 |

|   |     | 2.1.1 Cloud and edge computing                                  | 18 |

|   |     | 2.1.2 Network Function Virtualisation                           | 23 |

|   |     | 2.1.3 Programmable network hardware                             | 25 |

|   | 2.2 | Related works                                                   | 30 |

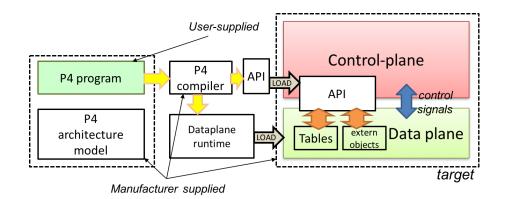

|   |     | 2.2.1 ClickNP                                                   | 30 |

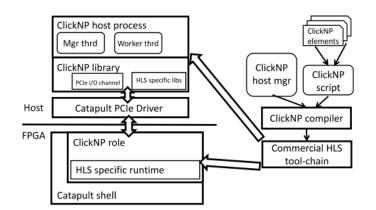

|   |     | 2.2.2 Azure Accelerated Networking (AccelNet)                   | 31 |

|   |     | 2.2.3 FLOEM                                                     | 33 |

|   |     | 2.2.4 Lambda-NIC                                                | 34 |

|   |     | 2.2.5 NICA                                                      | 34 |

|   |     | 2.2.6 iPipe                                                     | 35 |

|   |     | 2.2.7 FlowBlaze                                                 | 36 |

|   |     | 2.2.8 FairNIC                                                   | 37 |

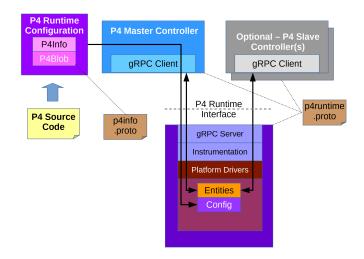

|   |     | 2.2.9 P4Runtime                                                 | 38 |

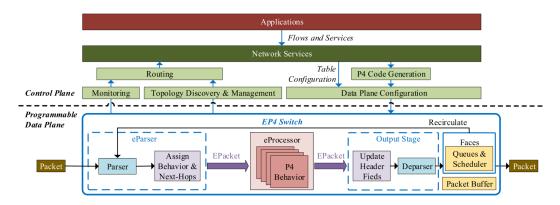

|   |     | 2.2.10EP4                                                       | 39 |

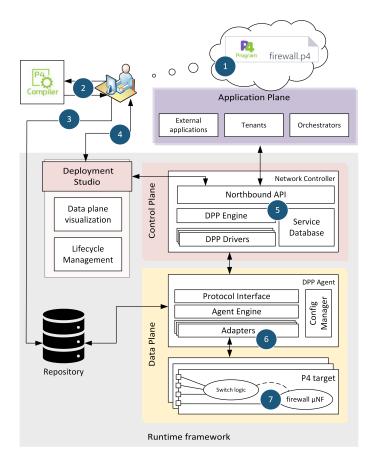

|   |     | 2.2.11DPPx                                                      | 40 |

|   | 2.3 | PIaFFE framework                                                | 42 |

|   | 2.4 | Chapter remarks                                                 | 44 |

| 3 | A f | ramework for flexible software/hardware co-design of in-network | s  |

|   |     | nputing                                                         | 45 |

|   | 3.1 | Overview                                                        | 45 |

|   | 3.2 | Proposal                                                        | 46 |

|   |     | 3.2.1 Design principles                                         | 46 |

|   | 3.3 | Architecture design and enablers                                | 51 |

|   |     | 3.3.1 Network programmability levels                            | 54 |

|   |     | PIaFFE automated deployment                                     | 55 |

|   | 3.5 | Chapter remarks                                                 | 57 |

| <b>4</b> | A c | o-design use-case on Network Function Virtualisation (NFV   | 7)   |     | <b>58</b> |

|----------|-----|-------------------------------------------------------------|------|-----|-----------|

|          | 4.1 | Overview                                                    |      |     | 58        |

|          | 4.2 | NFV use-case                                                |      |     | 59        |

|          |     | 4.2.1 Experimentation design                                |      |     | 59        |

|          |     | 4.2.2 Usage of the framework                                |      |     | 63        |

|          | 4.3 | Experimental evaluation                                     |      |     | 64        |

|          |     | 4.3.1 Experimentation setup                                 |      |     | 65        |

|          |     | 4.3.2 Testbed specification                                 |      |     | 65        |

|          |     | 4.3.3 Latency results                                       |      |     |           |

|          |     | 4.3.4 Throughput results                                    |      |     | 67        |

|          |     | 4.3.5 vCPU usage                                            |      |     |           |

|          | 4.4 | Chapter remarks                                             |      | ••• | 70        |

| 5        | Had | cking programmable data planes in cloud robotics: intercept | ing  | an  | d         |

|          | mo  | difying ROS messaging                                       |      |     | 71        |

|          |     | Overview                                                    |      |     |           |

|          | 5.2 | ROS use-case                                                |      |     |           |

|          |     | 5.2.1 Experimentation design                                |      |     |           |

|          |     | 5.2.2 Usage of the framework                                |      |     |           |

|          |     | 5.2.3 Background review                                     |      |     |           |

|          |     | 5.2.4 Vulnerabilities in programmable network devices       |      |     |           |

|          | 5.3 | Threat models exposed                                       |      |     |           |

|          |     | 5.3.1 In-network hijacking: man-in-the-middle attack        |      |     |           |

|          |     | 5.3.2 In-network replay attack                              |      |     |           |

|          | 5.4 | Chapter remarks                                             | •••  | ••• | 83        |

| 6        |     | viding data integrity by interacting and modifying raw pac  | kets | : a | n         |

|          | _   | A use-case                                                  |      |     | 84        |

|          |     | Overview                                                    |      |     |           |

|          | 6.2 | SHA use-case                                                |      |     |           |

|          |     | 6.2.1 Experimentation design                                |      |     |           |

|          |     | 6.2.2 Usage of the framework                                |      |     |           |

|          |     | 6.2.3 Functional decomposition for deployment               |      |     |           |

|          |     | 6.2.4 Multi-level forwarding between hardware and software  |      |     | 88        |

|          |     | 6.2.5 Hash algorithm implementation                         |      |     |           |

|          | 6.3 | Experimental evaluation                                     |      |     |           |

|          |     | 6.3.1 Benchmarking the virtualisation techniques            |      |     |           |

|          |     | 6.3.2 Experimentation setup                                 |      |     |           |

|          |     | 6.3.3 Results                                               |      |     |           |

|          | 6.4 | Chapter remarks                                             | • •  | ••• | 99        |

| 7        |     | v-latency passive optical networks (PON) through intercept  | ing  |     |           |

|          |     | difying DBA frames                                          |      |     | 100       |

|          | 7.1 | Overview                                                    |      | • • |           |

|          |     |                                                             |      |     |           |

|          | 7.2 | PON use-case                                                |      |     |           |

|          | 7.2 | PON use-case                                                | •••  | ••• | 101       |

|    |              | 7.2.3 Implementation details | )7 |  |

|----|--------------|------------------------------|----|--|

|    | 7.3          | Experimental evaluation      | )9 |  |

|    |              | 7.3.1 Experimental results   | )9 |  |

|    | 7.4          | Chapter remarks              | 11 |  |

| 8  | Con          | clusion and Future Works 11  | 2  |  |

|    | 8.1          | Thesis Summary               | 12 |  |

|    | 8.2          | Future Works                 | 13 |  |

|    | 8.3          | Final Remarks                | 14 |  |

| Bi | Bibliography |                              |    |  |

# Chapter 1

## Introduction

Recent years have seen a rapid increase in network interface bandwidth for data centre (DC) servers [DC 2015, Cloud 2016], outpacing the CPU computing power. For example, since 2009, Azure [Firestone 2017] has seen a 50x improvement in the network bandwidth in contrast with modest increases in CPU performance. Consequently, data-centre operators have to burn more CPU cores to fully utilise the network bandwidth, leaving fewer computing resources for tenant workload execution, increasing the cost of running cloud services, and adding latency and variability to network performance.

Edge computing has the potential to alleviate these constraints [Panicucci et al. 2020], aiming to bring cloud resources and services at the border of the network, as an intermediate layer between the end users and cloud data centres. By approximating the user to the cloud, network-related issues (e.g. packet loss, security and high latency) can be fixed for new applications, such as cloud robotics [Mello et al. 2019, Xie et al. 2019] and passive optical networks (PON) [Das et al. 2020].

Nevertheless, edge computing is an expensive architecture solution when compared to the cloud and may not be able to tackle a large set of latency-sensitive and critical applications in production environments. Thus, there is room for exploiting this demand for computational resources on the edge, by using state-of-the-art data plane programmability for co-design applications and hardware, reducing host CPU demand and improving latency requirements.

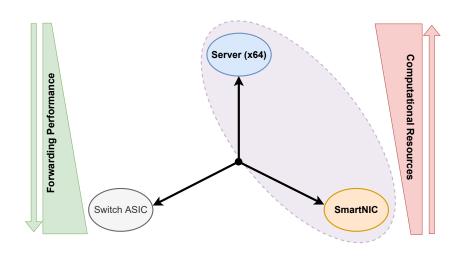

In-Network Computing (INC) is a promising field that aims at using the capabilities of programmable network devices, such as programmable switch ASICs and programmable network interface cards (aka SmartNICs), offloading computing from commodity servers to the programmable data plane [Rüth et al. 2018, Nour et al. 2020].

Emerging in-networking processor-based smart network interface cards (SmartNICs) (e.g., Netronome Agilio [NETRONOME 2019], Cavium LiquidIO [CAVIUM 2019], Mellanox BlueField [MELLANOX 2019]) offer a solution to offload the network traffic from traditional commodity servers (x86-64), providing a software development kit (SDK) for customising the data plane by use of domain-specific programming languages (e.g., P4, eBPF, etc.), expressing how packets should be processed into these programmable devices.

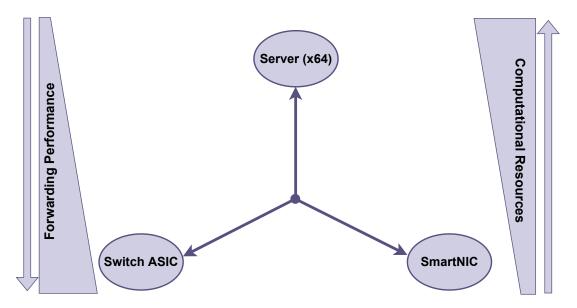

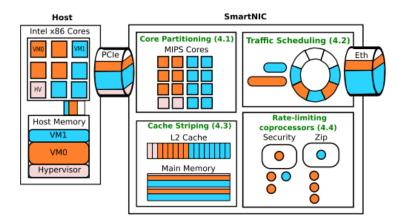

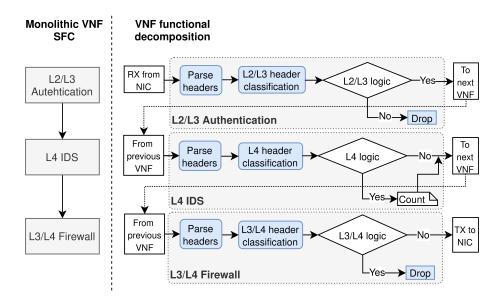

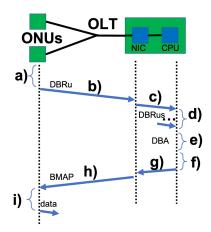

Figure 1.1 shows the architecture options for INC, highlighting the three main

architectural targets when prototyping (in-)network applications. In terms of forwarding performance and computational resources, the main characteristics are the following:

Figure 1.1: Architectural options to In-Network Computing for packets processing.

- i. **Traditional commodity servers**, with plenty of CPU and memory resources for processing network packets, but with restricted packet forwarding performance;

- Programmable switch ASIC, with multiple network physical ports and highperformance for forwarding packets, but with limited system resources, i.e., memory, CPU;

- iii. **SmartNIC (or FPGA-based) programmable device**, placed close to the commodity servers, which can boost up the offloading due to the shortest path to the *software layer*, however with the same limited computational resources as presented in programmable switch ASIC.

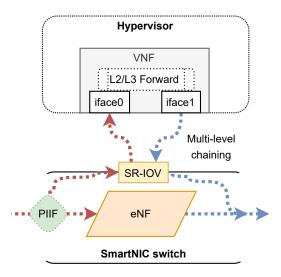

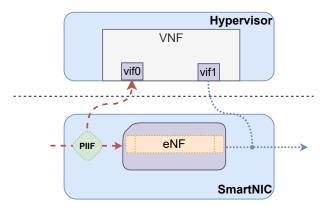

Traditionally, these three main architectures can be combined in order to achieve the aimed performance by offloading specific network function operations to meet the requirements of a large variety of applications. For example, in the Network Function Virtualisation (NFV) paradigm, a direct benefit of employing a SmartNICbased solution for edge computing is its physical placement in relation to the commodity servers, shorting the pathway between virtual network functions (VNF) implemented in software and their potential pairs implemented into the hardware data plane.

On that account, these INC capabilities allow commodity servers to offload limited amounts of simple but general computations onto the programmable NIC while keeping the support of complex application logic on the hosts. By offloading lightweight and frequently invoked operations from the host to its own programmable network device, we can accelerate cloud applications on edge, while reducing the host CPU load without sacrificing the program generality. However, this intuitive scenario is not trivial to be implemented considering that the following points should be addressed:

- a compact eNF (embedded Network Function) version from a traditional VNF (Virtual Network Function) or application using a domain-specific programming language that fits into a resource-limited programmable NIC;

- a proper mechanism for exchanging network traffic between software and hardware levels;

- the correct balance of network traffic that can be offloaded without degrading the system's performance.

Therefore, the first key issue to be addressed is how to fit a conventional VNF inside a resource-limited programmable network device. In this context, **func-tional decomposition** is the process of taking a complex process and breaking it down into its smaller, simpler parts [Rahman Chowdhury et al. 2019]. Consequently, a modular functional decomposition can be used to dissect a VNF, enabling the reconstruction of it as an eNF employing the P4 language.

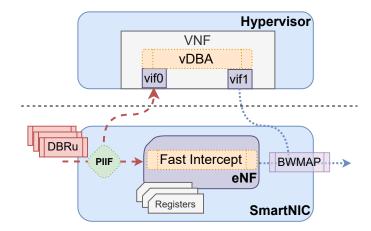

The next issue to be handled should be the communication between eNF and its VNF counterpart, as each is running in a different environment separated by PCI-e bus and system layers. As the network traffic data in the edge mainly flows from the NIC to the host itself (in contrast with DC networks, where VM traffic flows inside the host should be predominant), the rational choice is to create an **interception mechanism** inside the SmartNIC, which will be able to steer traffic between hardware and software levels, while following the application requirements.

Furthermore, merging the capabilities of software and hardware is another stone in the design and implementation process, as they have different constraints and resources. Hence, the **co-design** technique aims to incorporate hardware/software and exploit the synergy between the two, satisfying system load constraints, i.e., the correct proportion of offloading without overwhelming the overall system, including host CPU and SmartNIC hardware.

## **1.1 Research Question**

To tackle the aforementioned problems, this thesis aims to answer the following question:

• How to exploit co-design, i.e., between programmable network devices and end-host processing, opened by SmartNICs to accommodate diverse logic and their requirements considering different applications, including malicious ones, within the edge computing paradigm?

The co-design of applications presents an enormous challenge, as well as an opportunity, for network developers. By prototyping software-based network applications regarding the possibility of acceleration by offloading tasks to the data plane, developers can further explore the hardware capabilities in coexistence with their own applications, considering an offloading based on application/hardware requirements/constraints, leveraging edge computing by tackling concurrent resources within in-network computing.

Moreover, the co-design could be exploited (as we will reveal in cloud robotics security applications), creating a "tampered network device" which can compromise the network premises of a robot fleet by using malicious techniques for flooding or modifying the network traffic while flowing transparently through a customised data plane. Envisioning such a possibility, we can draw up a cryptographic network function embedded into the SmartNIC, ensuring data integrity by processing traffic data, and also saving CPU resources by offloading workload to the NIC.

## **1.2 Hypotheses**

In this thesis, we foresee the following hypotheses to tackle the described problem:

- **Hypothesis H1**: The suitable modular functional decomposition (identification and aggregation) is a key principle in matching the processing capacity of in-network computing, provided by the P4 language, to the specialised logic of applications.

- Justification H1: Since P4 language was not conceived with a modular functional decomposition method, porting oversized applications originally designed for the x86-64 architecture which relies on vast computational resources (memory and CPU) to a programmable network device can demand a lot of effort from the network developers. Functional decomposition urges simplifying this further migration or integration between applications and programmable data planes, easing the portability mainly by identifying the small functional parts of applications and giving a bird's-eye view of the network functions.

- **Hypothesis H2**: The lack of an architectural component for intercepting and interacting with raw packets is preventing innovative applications for in-network computing, other than the regular offloading of network flows onto SmartNICs.

- Justification H2: New complex and critical applications which can take advantage of edge computing, i.e. cloud robotics and passive optical networks, bring specific security and low latency requirements, as a minimum interference may disrupt the robot fleet operation or latency-sensitive applications. A programmable network device is a powerful tool, enabling the customisation of the packet processing/forwarding at a high-granularity level, but at the same time, raises concerns like: "what if that device has tampered"? A malicious attack could be delivered by a jeopardised device, compromising network security. By processing packets beyond the traditional network layers, or raw packet data, in-network computing can intercept/interact with the application layer, manoeuvring the end hosts according to its logic. At the same time, this characteristic also could be

used for leveraging network applications and building embedded network functions that can be able to interact with the network traffic data without the modification of their software/protocol counterpart.

## **1.3 Objectives**

To the best of our knowledge, we have not seen a state-of-art framework that covers this level of co-design and interaction between hardware and software applications using proper network programmable hardware and a domain-specific programming language. In order to tackle the defined research question and test the aforementioned hypothesis, this work has the following general objectives:

- To propose a framework that relies on modular functional decomposition (identification and aggregation) for flexible embedding network applications with their functionalities developed in P4 language and deployed into SmartNICs. The principle of co-designing will be demonstrated by an NFV use case.

- To introduce an architectural component in the framework for intercepting and/or interacting with raw packets, tackling security and performance aspects when using a programmable data plane.

- To demonstrate the framework by addressing diverse applications, such as cloud robotics applications, cryptographic hash functions and dynamic bandwidth allocation (DBA) in passive optical networks (PON).

## **1.4 Contributions**

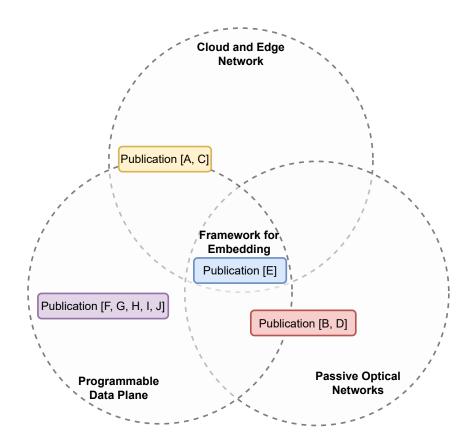

The proposal of this document was idealised through discussions and studies carried out in the LabNERDS-UFES and CONNECT Centre - Trinity College Dublin. Figure 1.2 gives an overview of how the publications are mapped to the different areas of interest in this thesis. The following contributions bring some clarification about the author's collaboration on each work, in reverse chronological order.

- Publication A: D.R. Mafioletti, M. Martinello, M. R. N. Ribeiro, M. Ruffini, F. Slyne, "To Embed or Not to Embed SHA in Programmable Network Interface Cards", in 18th International Conference on Network and Service Management (CNSM), 2022.

- Publication B: D.R. Mafioletti, F. Slyne, R. Giller, M. O'Hanlon, D. Coyle, B. Ryan, M. Ruffini, "Demonstration of a Low Latency Bandwidth Allocation Mechanism for Mission Critical Applications in Virtual PONs With P4 Programmable Hardware", in 2022 Optical Fiber Communications Conference and Exhibition (OFC), 2022, pp. 1-3.

- Publication C: D.R. Mafioletti, R. C. de Mello, M. Ruffini, V. Frascolla, M. Martinello, M. R. N. Ribeiro, "Programmable Data Planes as the Next Frontier

for Networked Robotics Security: A ROS Use Case", in 2021 1st Joint International Workshop on Network Programmability and Automation, 2021, doi: 10.23919/CNSM52442.2021.9615504.

- Publication D: D. R. Mafioletti, F. Slyne, R. Giller, M. O'Hanlon, B. Ryan, and M. Ruffini, "A Novel low-latency DBA for Virtualised PON implemented through P4 In-Network Processing", in Optical Fiber Communication Conference (OFC) 2021, P. Dong, J. Kani, C. Xie, R. Casellas, C. Cole, and M. Li, eds., OSA Technical Digest (Optical Society of America, 2021), paper F4I.2, doi: 10.1364/ OFC.2021.F4I.2.

- Publication E: D. R. Mafioletti, C. K. Dominicini, M. Martinello, M. R. N. Ribeiro and R. d. S. Villaça, "PIaFFE: A Place-as-you-go In-network Framework for Flexible Embedding of VNFs", ICC 2020 - 2020 IEEE International Conference on Communications (ICC), 2020, pp. 1-6, doi: 10.1109/ICC40277.2020.9149240.

Figure 1.2: Correlation between the main topics and publications of the thesis with the intersection between them.

The following publications, listed in reverse chronological order, were developed during the PhD and are not directly linked to this proposal. However, they helped to gain important knowledge in the matter and, therefore, should also be considered relevant contributions.

Publication F: R. S. Guimaraes, C. Dominicini, V.M.G. Martínez, B. M. Xavier, D. R. Mafioletti et al., "M-PolKA: Multipath Polynomial Key-based Source Routing

for Reliable Communications", in IEEE Transactions on Network and Service Management, doi: 10.1109/TNSM.2022.3160875.

- Publication G: C. Dominicini, R. S. Guimaraes, D. R. Mafioletti et al., "Deploying PolKA Source Routing in P4 Switches : (Invited Paper)", 2021 International Conference on Optical Network Design and Modeling (ONDM), 2021, pp. 1-3, doi: 10.23919/ONDM51796.2021.9492363.

- Publication H: R. S. Guimaraes, V. M. G. Martínez, R. C. Mello, D. R. Mafioletti, M. Martinello and M. R. N. Ribeiro, "An SDN-NFV Orchestration for Reliable and Low Latency Mobility in Off-the-Shelf WiFi", ICC 2020 - 2020 IEEE International Conference on Communications (ICC), 2020, pp. 1-6, doi: 10.1109/ICC40277.2020.9148900.

- Publication I: C. Dominicini, D. R. Mafioletti et al., "PolKA: Polynomial Keybased Architecture for Source Routing in Network Fabrics", 2020 6th IEEE Conference on Network Softwarization (NetSoft), 2020, pp. 326-334, doi: 10.1109/NetSoft48620.2020.9165501.

- Publication J: R. Valentim, C. K. Dominicini, R. S Villaça, M. Martinello, M. Ribeiro, D. R. Mafioletti, "RDNA Balance: Balanceamento de Carga por Isolamento de Fluxos Elefante em Data Centers com Roteamento na Origem", in Anais do XXXVII Simpósio Brasileiro de Redes de Computadores e Sistemas Distribuídos, 2019, pp. 1000-1013.

### **1.5 Text Structure**

The remainder of this Doctoral Thesis is divided as follows:

Chapter 2 presents in more detail the comparison with related works. It covers crucial concepts related to In-Network Computing, Network Function Virtualisation, and cloud and edge computing, including Cloud Robotics and Passive Optical Networks, which will be explored during the Thesis.

Chapter 3 gives the building blocks to construct a framework for embedding applications into a programmable network card, positioning it into the state of the art of existing network designs and computer architecture for the development and deployment of applications.

Chapter 4 presents the design and implementation of our framework proposal to support the implementation of virtual network function on a programmable network interface card, offloading the network packet processing and sharing the resources between hardware and software levels using an offloading balancer.

Chapter 5 shows a different perspective of the proposal, now tackling a more specific use-case: a cloud/edge infrastructure allied with cloud robotics applications based on Robotic Operating System (ROS), depicting the security concerns over a programmable data plane and the implications on the local network infrastructure and discussing the possibilities to overhaul this weakness.

Chapter 6 shows the feasibility of using an embedded application constructed using the PIaFFE framework to run a secure hash algorithm onto a programmable

network device, featuring new possibilities when offloading complex applications, in order to assure data security and reliability onto a limited-resources data plane.

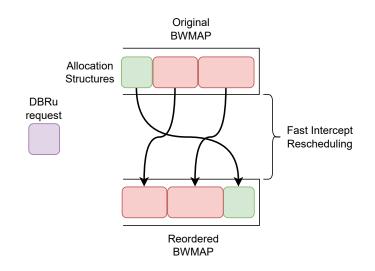

Chapter 7 leads to migration from specific network functions (e.g. firewall, NAT, etc.) and applications (e.g. cloud robotics and cryptography) to more generic applications but with a specific purpose, such as a high-level dynamic bandwidth allocation (DBA) algorithm on Passive Optical Networks (PON), although keeping the essence of sharing resources between hardware and software. This chapter also outset the first attempt to deliver the control of the network latency to an embedded network function based on instructions made available inside the own network frame/packet.

Chapter 8 draws a conclusion for the Doctoral Thesis discussing the next steps and future works.

## **Chapter 2**

## **Foundations and State-of-the-Art**

This chapter describes the position of this thesis with related works in the area of cloud and edge domains and programmable network hardware, as well as towards more specific domains, such as applications running into the data plane, tackling security concerns on cloud robotics, as well as possible solutions using cryptographic functions, and also improving low-latency requirements for passive optical networks (PON).

Firstly, Subsection 2.1.1 and 2.1.2 position the capabilities of the cloud and edge domains and NFV, showing the limitations of the current scenario and exposing what we envision to address these limitations.

Furthermore, in 2.1.1.2 and 2.1.2.1 rely on specific application domains, starting by describing the cloud robotics network paradigm, showing the points that we can take advantage of when using a high-level abstraction for exploring the lack of security on a programmable data plane. In this same direction, we propose the offloading of cryptographic hash functions for helping to assure the security and reliability of data, demonstrating that even a small-resource device can afford such complex applications using the proposed techniques and methods.

Moreover, in 2.1.1.1 we expose the current limitations of actual architecture, advancing to the constraints of using programmable network hardware on Passive Optical Networks (PON), in order to improve the scheduling mechanism on upstream data, delivering low-latency traffic for the required application/service through coprocessing PON frames inside the data plane.

To finish this chapter, in Subsection 2.1.3 we will discuss programmable network devices – which are one of the enablers of the proposal – and existing frameworks for programming and/or embedding the programmable data plane in Section 2.2, comparing them with the current proposal and showing the points on how the proposal differs from other existing works in 2.3.

## 2.1 Background

### 2.1.1 Cloud and edge computing

It is well known that cloud computing has been a promising architecture for nextgeneration networks once provides high flexibility resource virtualisation (e.g., servers with either CPU or GPU, networks, storage, and services) with cost-efficiency and centralised management [Le et al. 2016]. The cloud computing service models are categorised as Infrastructure as a Service (IaaS), Platform as a Service (PaaS), and Software as a Service (SaaS). They offer virtual resources (compute, storage, and network), software and development platforms (provided by the cloud infrastructure), and Internet-based applications (hosted on the cloud), respectively [Le et al. 2016].

As mentioned by [Nencioni et al. 2018], the possible future research challenges on softwarisation technologies such as NFV and SDN are the main enablers to develop novel solutions on top of new network generation (e.g., 5G network). The success of network virtualisation heavily relies on orchestrating end-controlling capabilities, which optimises the capital expenditure and operating costs (CAPEX and OPEX). In addition to the increasing softwarisation of infrastructure, content formats and production and consumption patterns are continuously changing as users demand improved Quality of Experience (QoE).

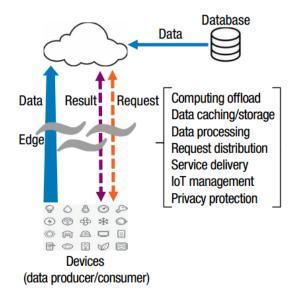

This trend requires adaptation processes that respond to aspects such as personalisation, localisation, interactivity, and mobility. Therefore, edge computing brings a new paradigm which shares computing, storage, and bandwidth resources as closely as possible with mobile devices or sensors. At the edge, the cloud services can deliver highly responsive time for local services [Satyanarayanan 2017]. The nodes at the edge DCs may perform many computing tasks, such as data processing, caching, service delivery, and privacy protection.

Figure 2.1: Edge computing paradigm. Source [Shi and Dustdar 2016].

ETSI defines the term Multi-Access Edge Computing (MEC) as a set of technologies that offers application developers and content providers cloud-computing capabilities and an IT service environment at the edge of the network, which extends the concept of edge cloud and can be used to assist C-RAN meeting the above 5G requirements. This environment is characterised by ultra-low latency and high bandwidth, as well as real-time access to radio network information that can be leveraged by applications [Sabella et al. 2019]. Those terms are viewed as necessary to enable specific use case classes defined, for instance, in 5G networks. MEC brings highly efficient cloud computing and storage capabilities at the edge and can be used by a RAN to offer low-latency and high-bandwidth data processing for latency-critical applications. It can also offer content caching near end users in order to alleviate the overall network load on data transmission through caching and forwarding content at the edge of the network [Das and Ruffini 2020].

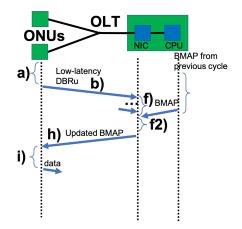

#### 2.1.1.1 Cloud Radio Access Networks with Passive Optical Networks

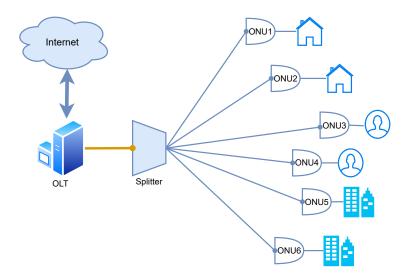

Passive optical networks (PON) are considered one of the prominent access network solutions due to the high capacity and coverage they can provide using a point-to-multipoint scheme that enables a single optical fibre to serve multiple premises using passive components. A typical PON architecture is constituted of a centralised Optical Line Terminator (OLT) and a number of Optical Network Units (ONUs) located at the premises, as shown in Figure 2.2.

Figure 2.2: A typical PON architecture.

Meanwhile, the high Capital expenditure (CAPEX) required for PON deployment has been an obstacle to large-scale adoption, especially in rural areas with a lower number of users and bandwidth demand. To this point, multiple solutions have been proposed in the past to improve the business case of access fibre deployments, stemming from changes in the overall network architecture to the development of cost-effective transceivers for multi-wavelength PONs [Cheng et al. 2014].

A complementary approach to economic sustainability is to increase the revenue generated by the PON by increasing the number and types of services that can be supported, for example, including mobile back-haul [Alvarez et al. 2016] and front-haul [Chanclou et al. 2013], in addition to the enterprise and residential applications. Therefore, a scenario in which all the aforementioned services can coexist and operate on the same PON infrastructure is pivotal in increasing the utilisation of the infrastructure, thus generating new revenue streams.

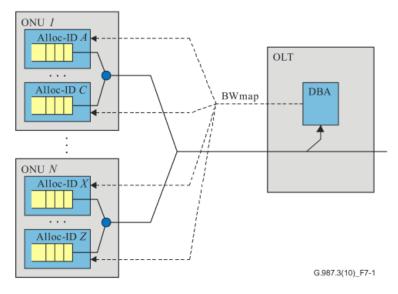

PON uses a dynamic bandwidth allocation (DBA) mechanism (Figure 2.3) to prevent collisions between simultaneous upstream transmissions of multiple ONUs. DBA methods have surfaced with strategies to share limited resources in optical access networks with a growing number of users. Over the years, these networks have also vastly improved by increasing their bandwidth. In addition, Quality of Service (QoS) parameters are incorporated into the bandwidth-sharing procedure.

Figure 2.3: PON DBA abstraction [ITU-T 2014].

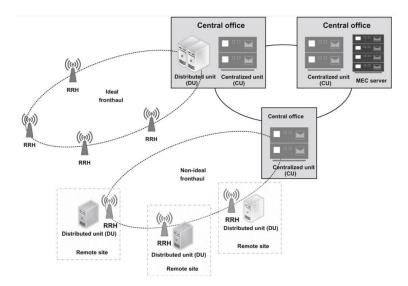

Cloud Radio Access Networks (C-RANs), along with functional split processing, are regarded as the most promising 5G radio technologies that support these requirements. In the 5G New Radio (5G-NR) architecture of C-RAN, the baseband processing functions are split into three parts: the central unit (CU), distributed unit (DU), and a remote unit (RU) [Das et al. 2020], as depicted by Figure 2.4.

Figure 2.4: CU/DU-based C-RAN architecture [Ahmadi 2019].

As 5G networks will bring progressive densification of mobile cells, the cost of the optical transport network will soar to unsustainable levels, if cells are connected through dedicated point-to-point fibre. In addition, point-to-point solutions provide little flexibility in redirecting RUs connectivity between edge cloud nodes during

migration events. For this reason, PON is being considered as a possible costeffective solution to support optical Mobile Fronthaul (MFH) transport, as it can use an already deployed Optical Distribution Network (ODN) to provide fronthaul transport for RUs along with serving residential users.

However, achieving low latency for using C-RAN and 5G is a major challenge for TDM-PONs in the upstream direction, because of the Time Division Multiple Access (TDMA) nature of the operation, which employs the DBA algorithm to provide the time slots for transmitting to each ONU on the system. Network function virtualisation could be used to help overcome this limitation, but the extra layers added by the software layers (e.g. OS, hypervisor) add more latency to the process, capping the benefits early noted. In-Network Computing must be an enabler for low-latency applications since the offloading of virtual network functions running inside a hypervisor onto a network data plane will cut these extra layers added before by the NFV paradigm.

#### 2.1.1.2 Cloud Robotics

Robotic systems have brought significant socioeconomic impacts to human lives over the past few decades. For example, industrial robots have been widely deployed in factories to execute various tasks, from repetitive ones to dangerous tasks. These programmed robots have been very successful in industrial applications due to their high endurance, speed, and precision in structured factory environments. To extend the functional range of these robots or to deploy them in unstructured environments, robotic technologies are integrated with network technologies to foster the emergence of networked robotics.

A networked robotic system refers to a group of robotic devices that are connected via a wired and/or wireless communication network. Networked robotics applications can be classified as either teleoperated robots or multi-robot systems. In the former case, a human operator controls or manipulates a robot at a distance by sending commands and receiving measurements via the communication network.

Networked robotics, similar to standalone robots, faces inherent physical constraints as all computations are conducted on board the robots, which have limited computing capabilities. Information access is also restricted to the collective storage of the network. With the rapid advancement of wireless communications and recent innovations in cloud computing technologies, some of these constraints can be overcome through the concept of cloud robotics, leading to more intelligent, efficient and yet cheaper robotic networks.

Cloud computing provides a natural venue to extend the capabilities of networked robotics. NIST [Mell et al. 2011] defines cloud computing as "a model for enabling ubiquitous, convenient, on-demand network access to a shared pool of configurable computing resources (e.g., networks, servers, storage, applications and services) that can be rapidly provisioned and released with minimal management effort or service provider interaction." Through its three service models (i.e., software, platform and infrastructure), it enables tremendous flexibility in designing and implementing new applications for networked robotics.

The Robot Operating System (ROS) was developed as a framework that provided

the software infrastructure for cloud robotics employment. As a framework, ROS provides a set of tools and libraries that simplify the task of creating a new robot and controlling it. Indeed, ROS is the most popular framework in robotics research and it also grows in terms of industrial use. This makes ROS a worthwhile target for attackers, especially since security is not addressed by the core framework itself, suffering from security issues due to its open architecture and flexibility project. These concerns could be increased if we bring the security flaw to the premises, based on a jeopardised device (e.g. a server or network device), assuming that these devices and the overall premises should be considered as a secure zone.

### 2.1.2 Network Function Virtualisation

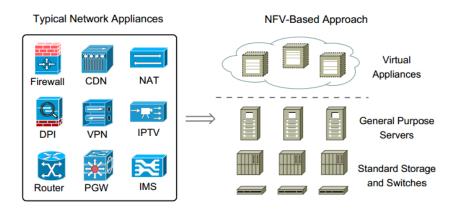

The presence of proprietary hardware-based network appliances, known as middleboxes, is a crucial part of the operation of today's computer and telecommunications networks. It supports a diverse set of network functions, such as firewalls, intrusion detection systems, load balancers, NAT, caches, and proxies [Martins et al. 2014]. For instance, in company networks, the number of these middleboxes is equivalent to the number of routers and switches deployed [Sherry et al. 2012].

However, the presence of these middle-boxes brings several problems, such as [Han et al. 2015]: networks have become very complex with a wide variety of proprietary elements; the time to bring new services and functionalities to the market is high, as it depends on the production of new hardware; the operation of the networks is costly and depends on specialised knowledge in each proprietary platform; the costs of acquiring equipment to meet network demands are high, but they quickly reach obsolescence; lack of flexibility and scalability, as resources, cannot be moved according to demands, and need to be scaled to the peak scenario; there are big barriers to innovation since it requires a significant investment to develop a device in hardware; the technologies of different manufacturers are incompatible with each other and do not allow reuse of hardware and software.

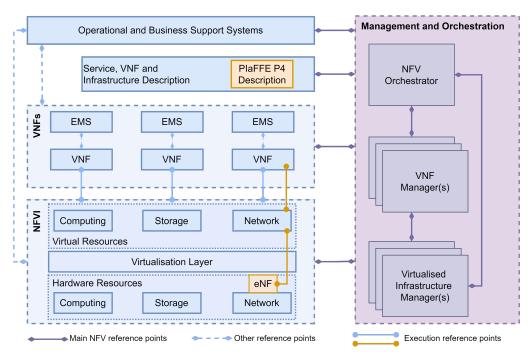

To address these problems and implement less costly and more flexible network infrastructure, NFV takes network functions of commercial appliances, actually dedicated hardware and software, to off-the-shelf equipment. By executing software-based functionality on commodity hardware with virtualisation technologies for processing, storage, and networking, as exemplified in Figure 2.5, NFV frees a wide range of innovative solutions for new networks.

The NFV objectives can be summarised as listed below [ETSI NFV ISG 2014]:

- Reduced CAPEX when compared to a specific target of hardware implementations: This goal is achieved by adopting commodity hardware and virtualisation techniques, reducing the number of different hardware architectures and resource sharing.

- Scalability and flexibility network functions: it is possible to decouple location from functionality and allocate network functions in the most appropriate places according to demands, increasing resiliency through visualisation, and making resource sharing easier. It becomes a strong groundbreaking mechanism for the next network generation as 5G networks.

Figure 2.5: NFV implementation of network functions using virtualisation techniques over standard hardware. Source: [Han et al. 2015].

- Software-based implementation: it incentives innovation and is time-consuming for creating a new product which reaches a specific market share.

- Reduced OPEX (operational expenses) by automating the procedures and making faster decisions for a specific event (e.g., fail, workload, and new demand).

- Reduced power consumption by migrating workloads and shutting down unused hardware.

- Interoperability through open and standardised interfaces between the network functions, the underlying infrastructure, and the associated management entities. In this way, the elements of NFV architecture can be implemented by different vendors.

These objectives have a huge impact on the business model of telecommunications networks, specifically in the new 5G networks. Consequently, this sector has received more investments in NFV standardisation, as discussed in the next section. However, it is essential to emphasise that the paradigm is applicable in both computer networks and telecommunications networks, especially at a time when both are converging to a resource-delivery model based on cloud computing.

### 2.1.2.1 Cryptographic hash functions

Cryptographic hash functions are one of the most important tools in the field of cryptography and are used to achieve a number of security goals like authenticity, digital signatures, pseudo number generation, digital time stamping and others.

Hash functions map a large collection of messages into a small set of message digests and can be used for error detection, by appending the digest to the message during the transmission. The error will be detected if the digest of the received message, on the receiving end, is not equal to the received message digest. With the advent of public key cryptography and digital signature schemes, cryptographic hash functions gained much more prominence. Using hash functions, it is possible to produce a fixed-length digital signature that depends on the whole message and ensures the authenticity of the message. To produce a digital signature for a message M, the digest of M, given by H(M), is calculated and then encrypted with the secret key of the sender [Sobti and Geetha 2012].

In order to provide security services, cryptographic hash algorithms need to guarantee some properties which are not necessarily guaranteed by general-purpose hash functions. The **one-way** or **preimage resistance** property of cryptographic hash functions implies that it is computationally infeasible to compute the message M given its hash DM(M). The **second preimage resistance** property means that, given a hash value DM(M), it is computationally infeasible to find a different message  $M' \neq M$  that yields the same hash value. The **pseudo-randomness** property means that the hash value of a message must expose statistical randomness. Finally, the **collision resistance** property means that it is computed in feasible to find a pair of messages M1 and M2 which produce the same hash value [Martino and Cilardo 2020].

The Secure Hash Algorithm (SHA) is a family of cryptographic hash functions defined by the National Institute of Standards and Technology (NIST) and published as the Federal Information Processing Standard (FIPS) 180, Secure Hash Standard (SHS). The algorithm is an iterative, one-way hash function that can process a variable-size message to produce a fixed-size condensed representation called a message digest. This algorithm enables message integrity verification, i.e., any change to the message will, with a very high probability, result in a different message digest. This property is useful in the generation and verification of digital signatures and message authentication codes, and in the generation of random numbers or bits [Dang et al. 2015]. The SHA-2 family of cryptographic hash functions was first announced in 2001 and includes SHA-224, SHA-256, SHA-384 and SHA-512, named according to the length of the message digest created by each one, suppressing the previous SHA-1 implementation due to security improvements.

As cryptographic hash functions are compute-intensive applications, which begs the question of extending P4, and its hardware platforms, into cryptographic algorithms. This would enable offloading secure applications/tasks to the data plane. The expected benefits are twofold: i) saving CPU resources for other applications running at the hypervisor and their tenants and ii) reducing latency and increasing the number of processed packets per time unit. The latter benefit will come from avoiding the operating system and hypervisor stacks in between the network and the SHA application.

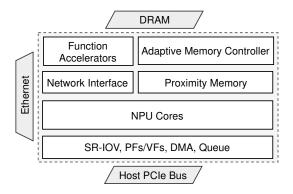

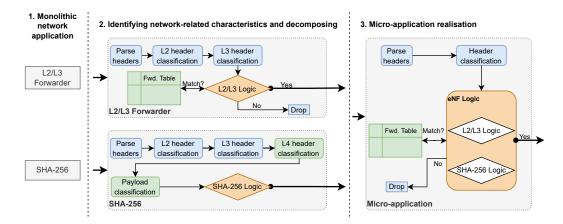

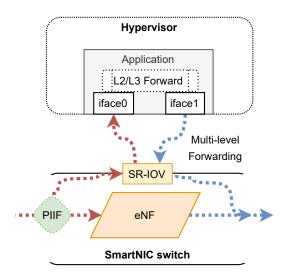

### 2.1.3 Programmable network hardware

There is paradoxically flexible FPGA-based hardware that is limited by its complex hardware description languages and powerful ASICs are limited by a reduced set of functionalities made available by their vendors. SmartNICs emerge as a compromise solution. Figure 2.6 shows the architecture of a typical SmartNIC with an in-networking processor [CAVIUM 2019, NETRONOME 2019]. It is basically comprised of a multi-core NPU (Networking Processor Unit), local memory and an SR-IOV (Single Root I/O Virtualisation) interface. These architectural components connect each other using a high-performance interconnection bus. They also provide on-chip/off-chip accelerators to speed up certain operations (e.g., encryption, hashing, look-ups, buffer management, etc).

Figure 2.6: SmartNIC architecture simplified block diagram.

In SR-IOV-compliant hardware, each host connects to a privileged physical function (PF), while each virtual machine connects to its own virtual function (VF). A VF is exposed as a unique hardware device to each VM, allowing the VM, and consequently, VNF resided therein, direct access to the actual hardware, and yet isolating VM data from other VMs. An SR-IOV-compliant SmartNIC also has an embedded switch to forward packets to the right VF based on the MAC address. In addition to SR-IOV, Network Processing Unit (NPU) brings programmability to the data path by using some high-level programming language, such as P4 language. All this combined and properly used, enables improved throughput, reduced CPU utilisation, low latency, and scalability.

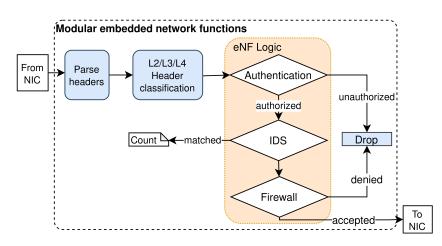

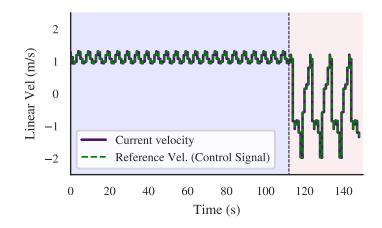

Despite the vast literature on offloading DC applications by in-network computing, few frameworks have tackled the NFV challenges. In particular, the state-of-the-art of NFV platforms has merely replaced monolithic hardware NFs with their monolithic software components. Interestingly, a large number of common functionalities (e.g., packet header parsing, packet classification, etc.) are repeated across different VNFs [Rahman Chowdhury et al. 2019]. Thus, our proposal brings its novelty by introducing a framework that allows programmers to decompose and deploy VNF applications to eNFs using a NIC-side in-networking processor.

#### 2.1.3.1 P4: Programming Protocol-Independent Packet Processors

Programming Protocol-independent Packet Processors (P4) is a domain-specific language for network devices, specifying how data plane devices (switches, NICs, routers, filters, etc.) process packets. P4 programs define how the various programmable blocks of a target architecture are programmed and connected. While P4 was initially designed for programming switches, its scope has been broadened to cover a large variety of devices, which are defined by the generic term *target*.

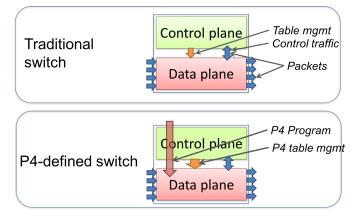

As a concrete example of a *target*, Figure 2.7 illustrates the difference between a traditional fixed-function switch and a P4-programmable switch. In a traditional switch, the manufacturer defines the data-plane functionality. The control plane controls the data plane by managing entries in tables (e.g. routing tables), configuring specialised objects (e.g. meters), and processing control packets (e.g. routing

protocol packets) or asynchronous events, such as link state changes or learning notifications [The P4 Language Consortium 2021].

Figure 2.7: Traditional switches vs. programmable switches [The P4 Language Consortium 2021].

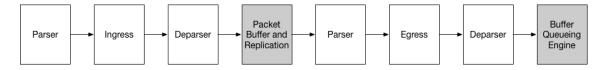

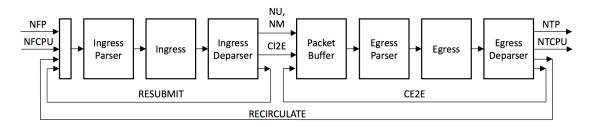

Portable Switch Architecture (PSA) Model is a target architecture that describes common capabilities of network switch devices that process and forward packets across multiple interface ports. The PSA Model has six programmable P4 blocks and two fixed function blocks, as shown in Figure 2.7. The behaviour of the programmable blocks is specified using P4 language. The Packet buffer and Replication Engine (PRE) and the Buffer Queuing Engine (BQE) are target-dependent functional blocks that might be configured for a fixed set of operations. [The P4.org Architecture Working Group 2020]

Figure 2.8: Portable Switch Pipeline [The P4.org Architecture Working Group 2020].

Incoming packets are parsed and validated, and then passed to an ingress match action pipeline, which makes decisions on where the packets go. The ingress *deparser* P4 code specifies the packet contents to be sent to the packet buffer, and what metadata related to the packet is carried with it. After the ingress pipeline, the packet may optionally be replicated (i.e. copies made to multiple egress ports), and then stored in the packet buffer. For each such egress port, the packet passes through an egress parser and match-action pipeline before it is *deparsed* and queued to leave the pipeline. Figure 2.9 shows all possible paths for packets that must be supported by a PSA implementation.

Figure 2.9: Packet paths in PSA [The P4.org Architecture Working Group 2020].

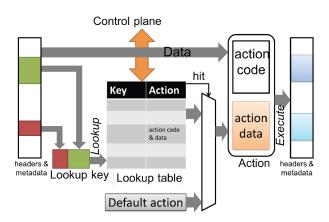

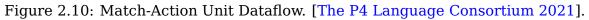

In P4, a table describes a match-action unit. The lookup table is a finite map whose contents are manipulated asynchronously (read/write) by the target controlplane, through a separate control-plane API. Syntactically a table is defined in terms of a set of key-value properties. The structure of a match-action unit is shown in Figure 2.10.

A P4-programmable target differs from a traditional device in two essential ways [The P4 Language Consortium 2021]:

- The data plane functionality is not fixed in advance but is defined by a P4 program. The data plane is configured at initialisation time to implement the functionality described by the P4 program (shown by the long red arrow) and has no built-in knowledge of existing network protocols.

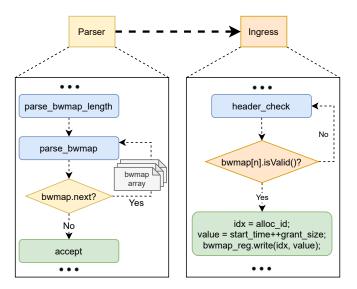

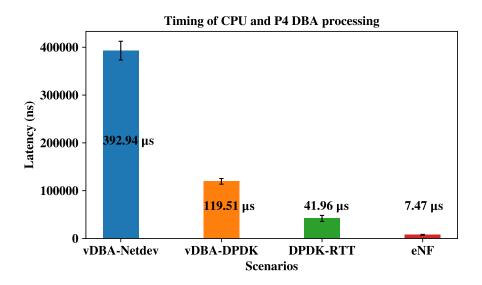

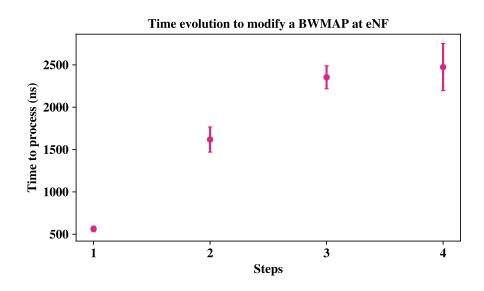

- The control plane communicates with the data plane using the same channels as in a fixed-function device, but the set of tables and other objects in the data plane is no longer fixed since they are defined by a P4 program. The P4 compiler generates the API that the control plane uses to communicate with the data plane.